## Tut 14 (Tutor) 2nd Edition

Monday, 4. February 2019 20:59

- O. ORGANISATORISCHES 3. Block - Test • Zeit bis So. 10.02. 19 23 59 ▲ Klausur 27.02.19 (Mi) 0800, Anneldung 10.02. - 20.02 über MOSES & <u>aispos</u> ?! · Seit den 04.02. (Mo) ist die Probeklausur verfügbar - Bearbeiter bis nöchste Woche (empfohlen), Q&A nächste Woche. Mehr auf Treitagsrunde 1. DIE ALU · Letzte Woche : Schaltungen konstnuert, un Aufgaben & Funktionen zu erfüllen - 2.3. Prinzahlerkennung · Computerprozessor setzt sich aus Logikgatter zusammer · Rechenwerk, Steverwerk, Speicher... · Recherwerk CALU) führt Berechnungen aus, u.a. Addition 1.1. Halbaddierer · Wie sieht so ein <u>Addierwerk</u> aus? · Addieren eines Bits ALU: Halbaddierer 2 <u>NT</u> (1 <u>1</u> Bit Addition ×y|cs 00 00 0 1 01 10 01 10 11 3 Log. Ausdrücke Schaltplan s= ×⊕y

- Ein Halbaddierer setzt sich einfach aus einem XOR & AND zusammen ?

Mehrere Bits addieren.

0 1 1 0 + 0 0 1 1 - 0 1 1 - 0 1 1 - 0 1

$C = X \cdot y$

• Funktioniert nicht, weil wir nur zwei Eingangsbits haben

• Doof : wie konn das Carry in berücksichtigt werden ?

1.2 Der Volladdierer

· Zielsetzung durch Wertetabelle ALU: Volladdierer • Ziel: Carry in berücksichtigen ? ... lässt sich aus Wertetabelle ZHA und 1 OR Cin × Y S Cout bauen 🏅 - HAC ≥1 - Couct Y HAS -0 S -• S 0 0 1 FA 📃 1 1 - Cout 1 1 1 · Zusätzlicher Eintrag für den alten Übertrag (Carry-In) · Wird aus zwei HA und einem OR-Gatter zusammengesetzt · Logische Ausdrücke:  $\rightarrow$  s = (x  $\oplus$  y)  $\oplus$  Cin - Court =  $x \cdot y + (Cin \cdot (x \oplus y))$ • Nur könner wir zwei 4 Bit zahler bepw. durch Kaskadierung von 4 Volladdierer addieren • Bild : was ist Cino ? - = OV, auf GND gelegt, da eh kein Carry In . · Ende des reg. Stoffes 1.3 ALU-Entwurf

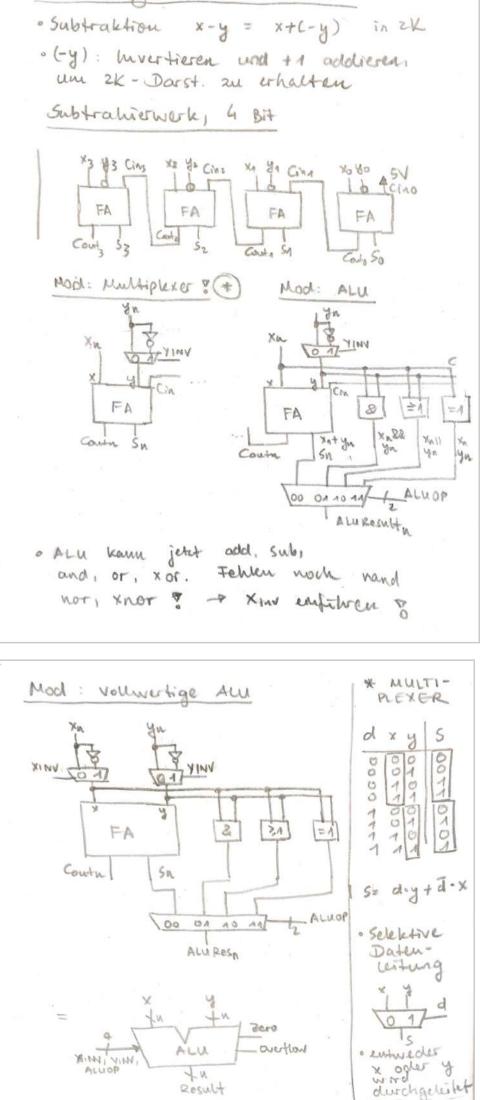

Erweiterung d. 4-Bit Addierers: · Subtraktion x-4 = x+(-4) in 2K

Spercher S = 5,40 S = 5,40 Q = 7-FF : Toggle bei 1 in